I’m an AI chip architect on Apple’s

Neural Engine

hardware-architecture team, where I design architectures of AI

accelerators, shape the AI compiler and anaylze cutting edge AI workloads

for the A-, M-, and S-series SoCs (iPhone, Mac, Vision and Watch).

I hold a B.E. from Tsinghua University and an M.S. and Ph.D. from

the University of Michigan, Ann Arbor.

I am open to building meaningful professional connections in AI-chip

architecture and any other related fields.

Please connect with me on LinkedIn.

Please Note:

-- I do not provide referrals or discuss Apple-specific information.

-- I am not open to any discussion on paper-oriented research.

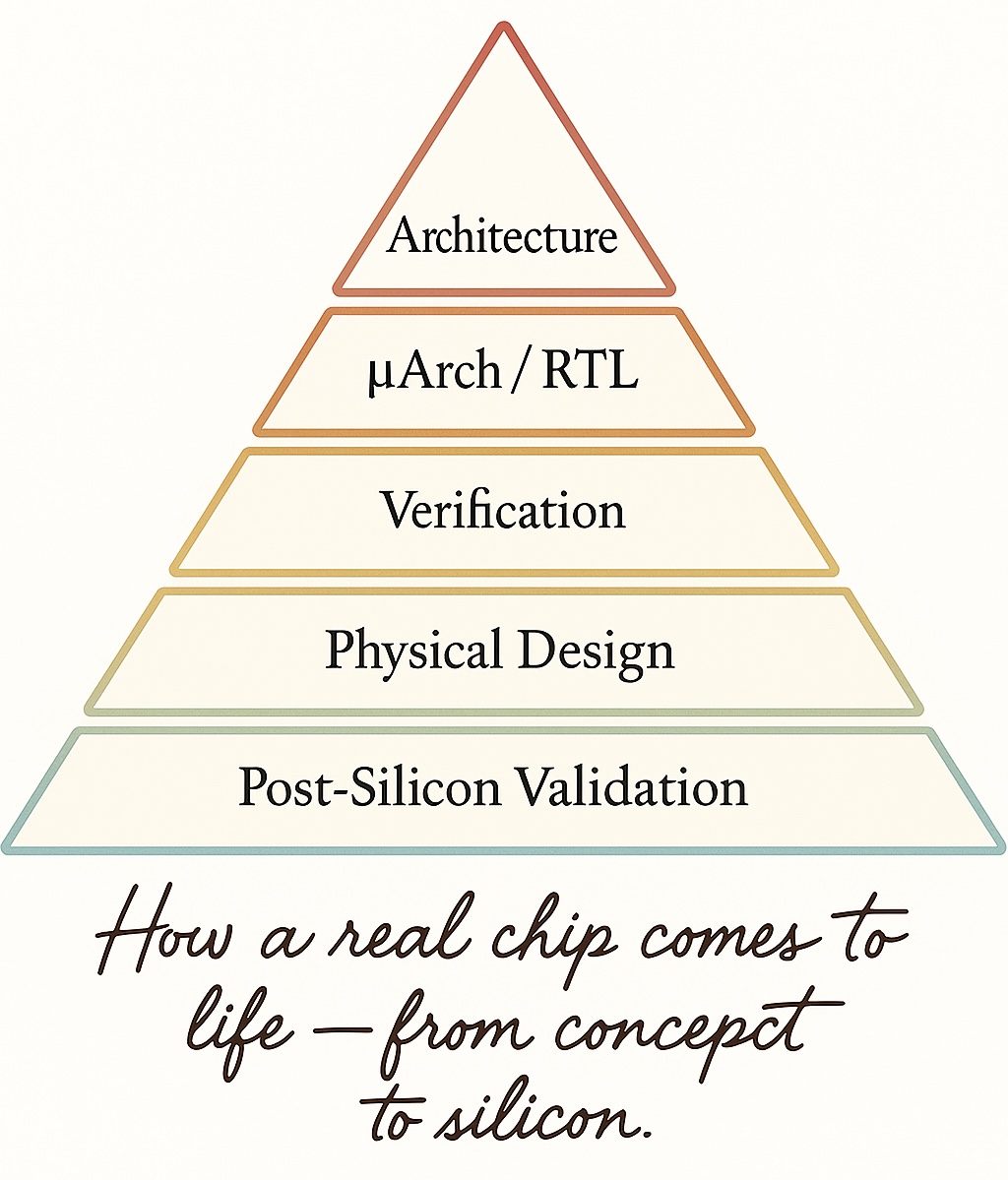

Crafting scalable, power-efficient silicon blocks that turn every AI task into seamless real-time experiences

Translating neural networks into hardware kernels, tuning compute and memory in harmony

Profiling models to surface bottlenecks and orchestrate performance and power in balance